# DANIEL FRANCO LEAL

IMPLEMENTAÇÃO DE CONTROLE DE CORRENTE POR HISTERESE DIGITAL

COM LIMITAÇÃO DA FREQUÊNCIA DE COMUTAÇÃO EM UM INVERSOR NPC

TIPO G PARA ACIONAMENTOS DE MÉDIA TENSÃO

# DANIEL FRANCO LEAL

# IMPLEMENTAÇÃO DE CONTROLE DE CORRENTE POR HISTERESE DIGITAL COM LIMITAÇÃO DA FREQUÊNCIA DE COMUTAÇÃO EM UM INVERSOR NPC TIPO G PARA ACIONAMENTOS DE MÉDIA TENSÃO

Dissertação submetida à banca examinadora designada pelo colegiado do Programa de Pós-Graduação em Engenharia Elétrica do Centro Federal de Educação Tecnológica de Minas Gerais e da Universidade Federal de São João Del Rei, como parte dos requisitos necessários à obtenção de grau Mestre em Engenharia Elétrica.

Orientador: Marcelo Martins Stopa

Coorientador: Alex-Sander Amável Luiz

Leal, Daniel Franco

L435i Implementação de controle de corrente por histerese digital com limitação da frequência de comutação em um inversor NPC tipo G para acionamentos de média tensão / Daniel Franco Leal. – 2023.

89 f.: il., gráfs, tabs., fotos.

Dissertação de mestrado apresentada ao Programa de Pós-Graduação em Engenharia Elétrica em associação ampla entre a UFSJ e o CEFET-MG.

Orientador: Marcelo Martins Stopa..

Coorientador: Alex-Sander Amável Luiz..

Banca examinadora: Marcelo Martins Stopa, Alex-Sander Amável Luiz, Allan Fagner Cupertino, Thiago Morais Parreiras, Lenin Martins Ferreira Morais. Dissertação (mestrado) – Centro Federal de Educação Tecnológica de Minas Gerais.

Inversores elétricos – Teses.

Correntes elétricas – Controle eletrônico – Teses.

Histerese – Teses.

Conversores de correntes elétricas – Teses.

Modulação de duração de pulso – Teses.

Stopa, Marcelo Martins. II. Luiz, Alex-Sander Amável. III. Centro Federal de Educação Tecnológica de Minas Gerais. IV. Universidade Federal de São João del-Rei. V. Título.

CDD 621.3815322

Elaboração da ficha catalográfica pela bibliotecária Jane Marangon Duarte, CRB 6º 1592 / Cefet/MG

# DANIEL FRANCO LEAL

# IMPLEMENTAÇÃO DE CONTROLE DE CORRENTE POR HISTERESE DIGITAL COM LIMITAÇÃO DA FREQUÊNCIA DE COMUTAÇÃO EM UM INVERSOR NPC TIPO G PARA ACIONAMENTOS DE MÉDIA TENSÃO

Dissertação submetida à banca examinadora designada pelo colegiado do Programa de Pós-Graduação em Engenharia Elétrica do Centro Federal de Educação Tecnológica de Minas Gerais e da Universidade Federal de São João Del Rei, como parte dos requisitos necessários à obtenção de grau Mestre em Engenharia Elétrica.

Trabalho aprovado em 6 de outubro de 2023.

| Comissão examinad | dora:                                                  |

|-------------------|--------------------------------------------------------|

| _                 | Prof. Dr. Marcelo Martins Stopa<br>Orientador          |

|                   | Prof. Dr. Alex-Sander Amável Luiz<br>Coorientador      |

| _                 | Prof. Dr. Allan Fagner Cupertino Convidado 1           |

| _                 | Prof. Dr. Thiago Morais Parreiras<br>Convidado 2       |

| _                 | Prof. Dr. Lenin Martins Ferreira Morais<br>Convidado 3 |

|                   | Belo Horizonte, MG                                     |

Belo Horizonte, MG

2023

# **AGRADECIMENTOS**

Agradeço à minha família e amigos que tanto me incentivaram nessa jornada. Agradeço aos meus orientadores, professor Stopa e professor Alex-Sander, por toda a dedicação e paciência que sempre tiveram comigo ao longo dos últimos anos. Ao CEFET-MG e ao PPGEL pela oportunidade, e ao grupo de pesquisa LEACOPI pelo acolhimento.

# **RESUMO**

Nas grandes indústrias, como siderurgia e mineração, por exemplo, os inversores de frequência devem ser capazes de operar na faixa de média tensão e alta potência. Desse modo, os inversores multiníveis têm uma importância significativa em acionamentos nessa faixa de operação. Suas vantagens incluem um melhor espectro de frequência das tensões e correntes de saída, redução das perdas por comutação e redução do estresse sofrido pelos interruptores eletrônicos. Neste sentido, o conversor Neutral Point Clamped (NPC) cumpre bem esse papel. Essa topologia está consolidada no mercado, e é muito importante em acionamentos de alta potência. Ela possui algumas variações, como por exemplo o NPC Tipo G, que fornece cinco níveis de tensão de fase na saída do conversor. As técnicas de controle e comutação aplicadas a esses inversores são um fator determinante no comportamento da tensão sintetizada. Este trabalho propõe o desenvolvimento, implementação e avaliação experimental de uma estratégia de comutação que utiliza a histerese de corrente. O acionamento é realizado de forma digital, ou seja, os sinais medidos e utilizados no controle são amostrados. Assim, é comum utilizar-se da frequência de amostragem para limitar a frequência de comutação dos interruptores eletrônicos, já que a frequência máxima de atuação é metade da frequência de amostragem. Baixas taxas de amostragem, por outro lado, diminuem a eficácia do controle, além de causar problemas no comportamento da histerese de corrente operando em conversores multiníveis. Dessa forma, esta pesquisa propõe uma forma de utilizar a histerese de corrente com altas taxas de amostragem, utilizando-se um circuito limitador de frequência nos sinais de comando dos interruptores eletrônicos. Essa técnica dissocia a frequência de amostragem da frequência de atuação, melhorando o funcionamento do modulador e diminuindo a distorção harmônica total da tensão e da corrente do inversor. Essas características são comprovadas através de resultados coletados na implementação do acionamento através de simulação computacional e experimentação em laboratório.

**Palavras-chave**: Inversor multinível; Controle de corrente; Histerese; Neutral Point Clamped (NPC); Pulse Width Modulation (PWM).

## **ABSTRACT**

In heavy industries such as steel and mining, for example, frequency inverters must be able to operate in the medium voltage and high power range. Thus, multilevel inverters have a significant importance in drives in this kind of operation. Its advantages include a better frequency spectrum of output voltages and currents, reduction of switching losses and the stress suffered by electronic switches. In this sense, the Neutral Point Clamped (NPC) converter fulfills this role well. This topology is consolidated in the market, and is very important in high power drives. It has some variations, such as the NPC Type G, which provides five levels of phase voltage at the output of the converter. The control and switching techniques applied to these inverters are a determining factor in the behavior of the synthesized voltage. This work proposes the development, implementation and experimental evaluation of a switching strategy that uses the current hysteresis. The drive is performed digitally, wich means that, the signals measured and employed in the control are sampled. Thus, it is common to use the sampling frequency to limit the switching frequency of electronic switches, since the maximum actuation frequency is half the sampling frequency. Low sampling rates, on the other hand, decrease control effectiveness, and cause problems in current hysteresis behavior operating in multilevel converters. In this sense, this research proposes a way to implement the current hysteresis with high sampling rates, using a frequency limiting circuit in the control signals of the electronic switches. This technique dissociates the sampling frequency from the actuation frequency, improving the operation of the modulator and reducing the total harmonic distortion of the inverter voltage and current. These characteristics are confirmed by results collected in the implementation of the drive through computer simulation and laboratory experimentation.

Key-words: Multilevel inverters; Current control; Hysteresis; Neutral Point Clamped (NPC); Pulse Width Modulation (PWM).

# **LISTA DE FIGURAS**

| Figura 1 – (a) Conversor meia ponte de dois níveis trabalhando como inversor           |

|----------------------------------------------------------------------------------------|

| monofásico e (b) seu circuito de comando com histerese de corrente20                   |

| Figura 2 – (a) Comportamento das formas de onda de tensão e corrente sintetizadas      |

| na saída do inversor monofásico comandado por histerese de corrente e (b) o sinal de   |

| erro da corrente aplicado no elemento de histerese21                                   |

| Figura 3 – (a) Esquema de um inversor multinível meia-ponte e (b) forma de onda        |

| típica da tensão de saída em degraus29                                                 |

| Figura 4 – Inversor de 3 níveis tipo NPC30                                             |

| Figura 5 – (a) Sinais de comando dos interruptores eletrônicos do braço referente à    |

| fase U, (b) formas de onde de saída de tensão entre os terminais de saída e o ponto    |

| neutro e (c) tensão entre dois terminais de saída u-v do inversor NPC 3 níveis (tensão |

| de linha)31                                                                            |

| Figura 6 – (a) Braço de um inversor a diodos de quatro níveis e (b) um de cinco níveis |

| e (c) um inversor de sete níveis com grampeamento a diodo32                            |

| Figura 7 – (a) Configuração do circuito de potência do inversor NPC Tipo G e (b) seu   |

| módulo ponte H, formado por dois braços de um inversor NPC três níveis33               |

| Figura 8 – Inversor de frequência de média tensão modelo MVW01 da WEG34                |

| Figura 9 – Esquema do circuito de potência do inversor Toshiba modelo Dura-Bilt5       |

| MV34                                                                                   |

| Figura 10 – Componentes d e q das correntes do motor referencial rotativo síncrono     |

| como o fluxo do rotor37                                                                |

| Figura 11 - Sistema básico de orientação indireta de campo em máquina de indução       |

| usando um modulador PWM regulado por corrente37                                        |

| Figura 12 - Diagrama completo do acionamento da máquina de indução por inversor        |

| NPC 5 níveis, comandado por histerese de corrente multifaixa e com controle vetoria    |

| por orientação de campo38                                                              |

| Figura 13 – Bloco desacoplador de tensão39                                             |

| Figura 14 – Controlador de velocidade40                                                |

| Figura 15 – Resposta em frequência da rigidez dinâmica com malha de velocidade e       |

| nosicão                                                                                |

| Figura 16 - Comportamento do controle por histerese de corrente multifaixa em um                  |

|---------------------------------------------------------------------------------------------------|

| conversor de cinco níveis44                                                                       |

| Figura 17 – Circuito de comando do controle por histerese de corrente multifaixa45                |

| Figura 18 – Corrente e tensão de um conversor com modulação por histerese de                      |

| corrente multifaixa46                                                                             |

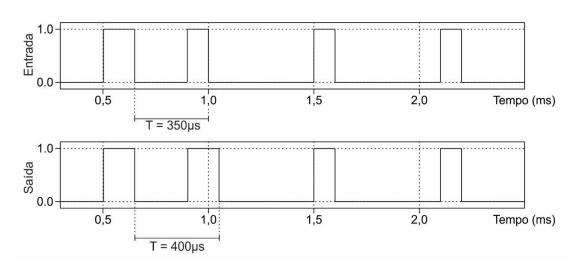

| Figura 19 – (a) Comportamento da histerese multifaixa com uma frequência de                       |

| amostragem baixa, insuficiente para o funcionamento adequado e (b) com uma                        |

| frequência de amostragem mais alta, que proporciona melhor aproveitamento da                      |

| técnica48                                                                                         |

| Figura 20 - Circuito limitador de frequência49                                                    |

| Figura 21 – Comportamento do circuito limitador de frequência50                                   |

| Figura 22 – Esquema do processamento do acionamento51                                             |

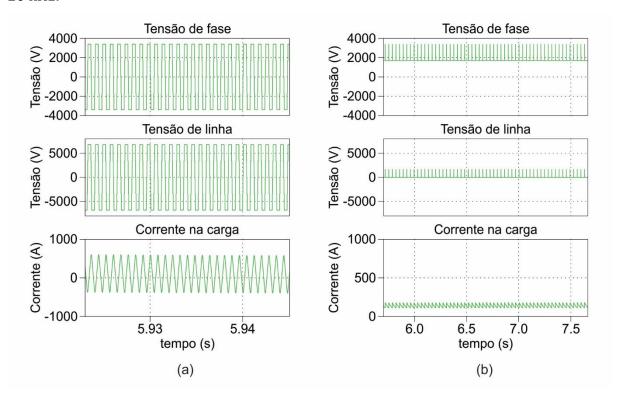

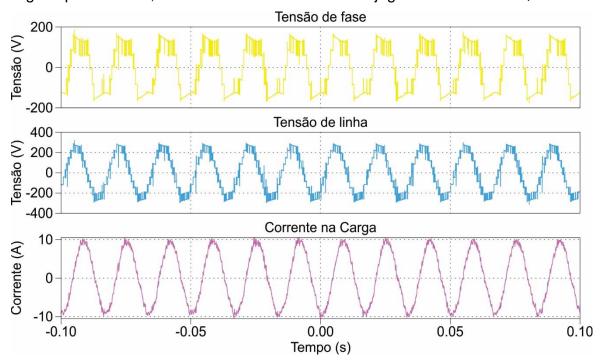

| Figura 23 - Tensão da fase a, tensão de linha V <sub>ab</sub> e corrente no motor durante o       |

| período para estabelecimento do fluxo para (a) a situação onde a frequência de                    |

| amostragem é de 5 $kHz$ e para (b) o segundo caso com frequência de amostragem c                  |

| 20 <i>kHz</i> 54                                                                                  |

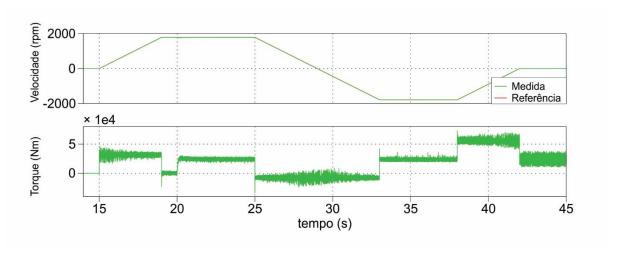

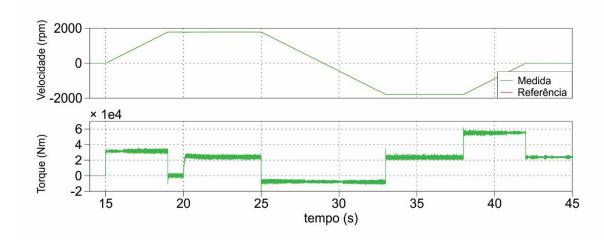

| Figura 24 – Velocidade do rotor e conjugado (estimado) para o acionamento do moto                 |

| com modulação por histerese de corrente multifaixa com frequência de amostragem                   |

| de 5 <i>kHz</i> 55                                                                                |

| Figura 25 – Velocidade do rotor e conjugado (estimado) para o acionamento do motor                |

| com modulação por histerese de corrente multifaixa com frequência de amostragem                   |

| de 20 $kHz$ e circuito limitador de frequência55                                                  |

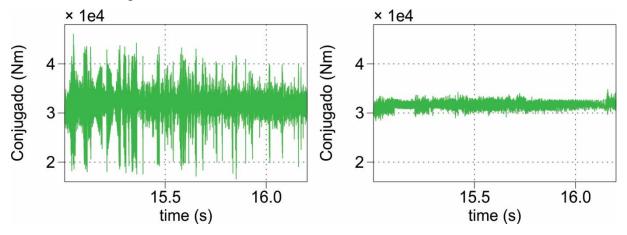

| Figura 26 – Detalhe da oscilação do conjugado durante a aceleração da máquina para                |

| (a) o acionamento com taxa de amostragem de 5 $kHz$ e (b) para o acionamento com                  |

| taxa de amostragem de 20 $kHz$ 56                                                                 |

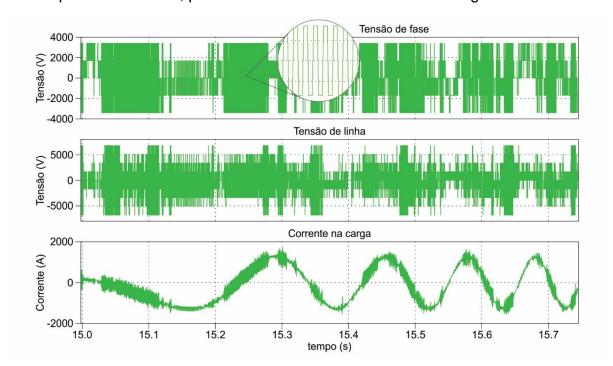

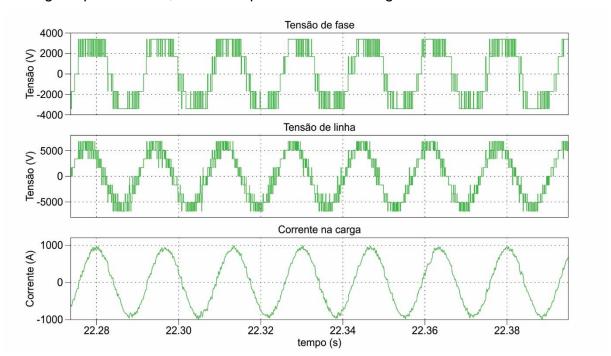

| Figura 27 – Tensão da fase a, tensão de linha V <sub>ab</sub> e corrente no motor para a operação |

| em rampa de velocidade, para acionamento com taxa de amostragem de 5 $kHz.57$                     |

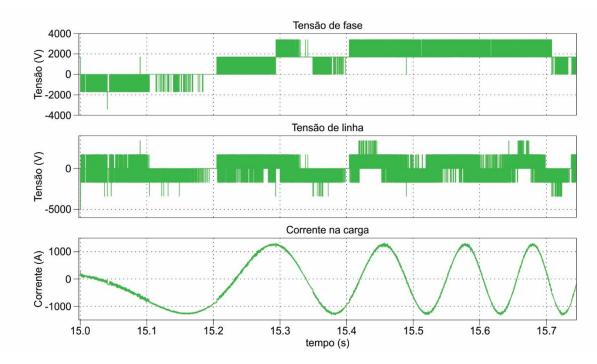

| Figura 28 – Tensões da fase a, tensão de linha V <sub>ab</sub> e corrente no motor para a         |

| operação em rampa de velocidade, para acionamento com taxa de amostragem de                       |

| 20 <i>kHz</i> 57                                                                                  |

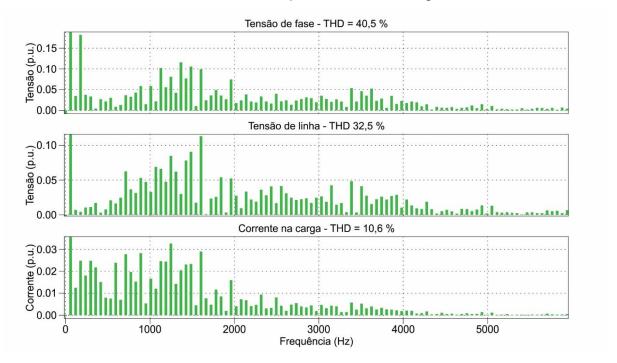

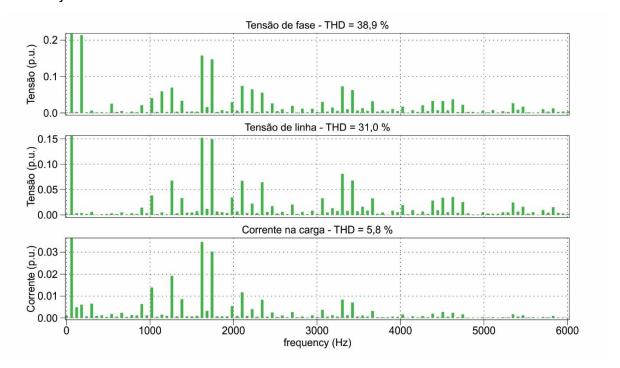

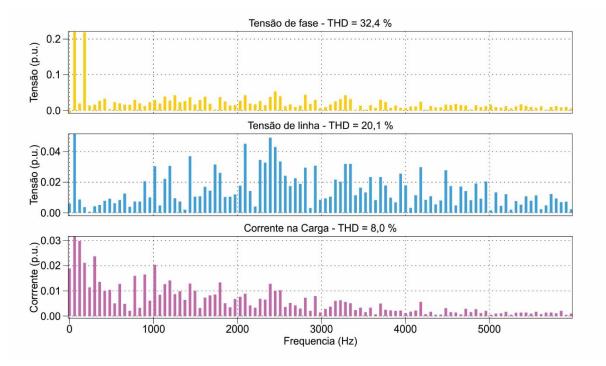

| Figura 29 – Espectro harmônico dos sinais da tensão da fase a, tensão de linha Vab e              |

| corrente no motor, em operação em regime permanente, para o acionamento por                       |

| histerese de corrente multifaixa com frequência de amostragem de 5 $kHz$ 59                       |

|                                                                                                   |

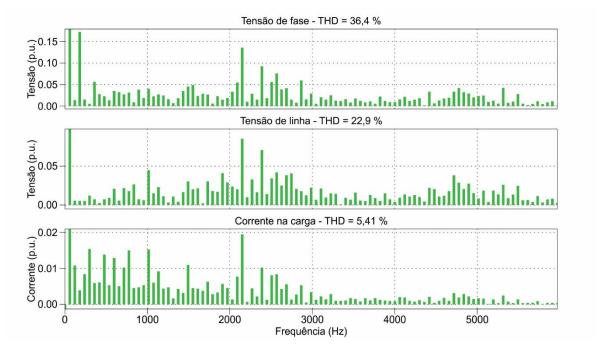

| Figura 30 – Espectro harmônico dos sinais da tensão da fase a, tensão de linha V <sub>ab</sub> e       |

|--------------------------------------------------------------------------------------------------------|

| corrente no motor, em operação em regime permanente, para o acionamento por                            |

| histerese de corrente multifaixa com frequência de amostragem de 20 $kHz$ e com                        |

| circuito limitador de frequência60                                                                     |

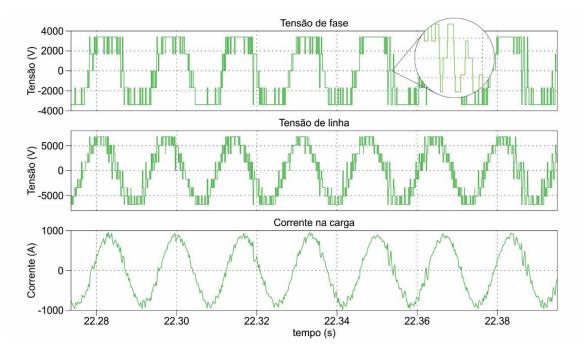

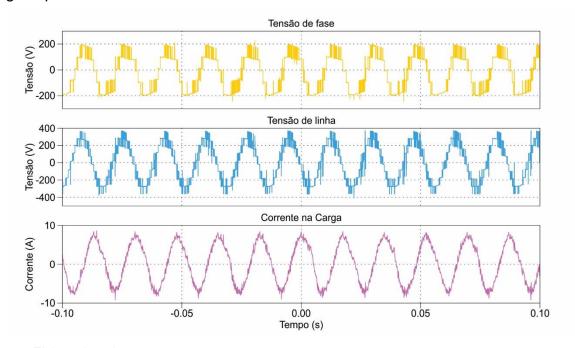

| Figura 31 – Tensão na fase a, tensão de linha V <sub>ab</sub> e corrente no motor em operação          |

| em regime permanente, com a frequência de amostragem de 5 $kHz$ 60                                     |

| Figura 32 - Tensão da fase a, tensão de linha V <sub>ab</sub> e corrente no motor em operação          |

| em regime permanente, com a frequência de amostragem de $20\ kHz.$ 61                                  |

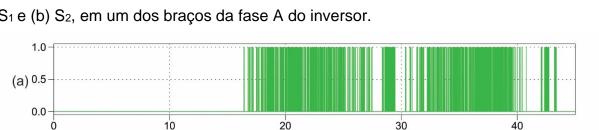

| Figura 33 – Atuação do circuito limitador de frequência para o (a) interruptor eletrônico              |

| S <sub>1</sub> e (b) S <sub>2</sub> , em um dos braços da fase A do inversor61                         |

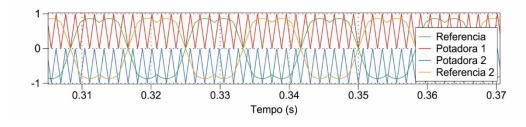

| Figura 34 – Sinais para geração dos comandos para modulação SVPD-PWM62                                 |

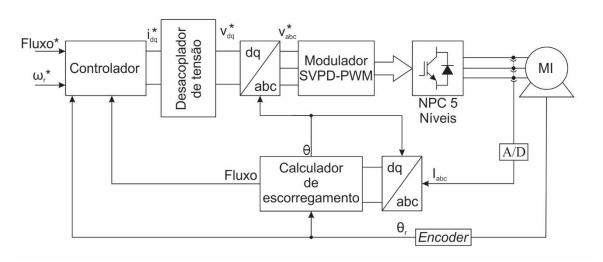

| Figura 35 - Diagrama completo do acionamento da máquina de indução por inversor                        |

| NPC 5 níveis, comandado por modulador SVPD-PWM e com controle vetorial por                             |

| orientação de campo63                                                                                  |

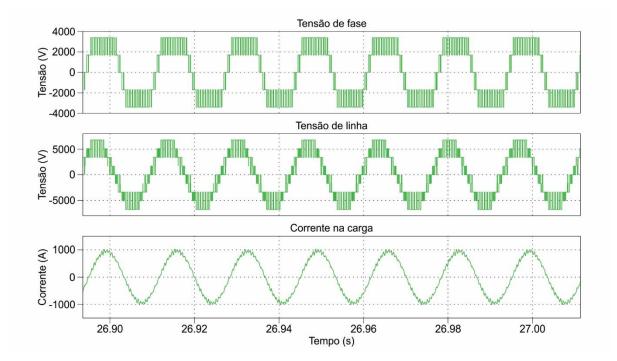

| Figura 36 - Tensão da fase a, tensão de linha $V_{ab}$ e corrente no motor em operação                 |

| em regime permanente, com modulação SVPD-PWM64                                                         |

| Figura 37 - Espectro harmônico dos sinais da tensão da fase a, tensão de linha $V_{ab}$ e              |

| corrente no motor, em operação em regime permanente, para o acionamento com                            |

| modulação SVPD-PWM65                                                                                   |

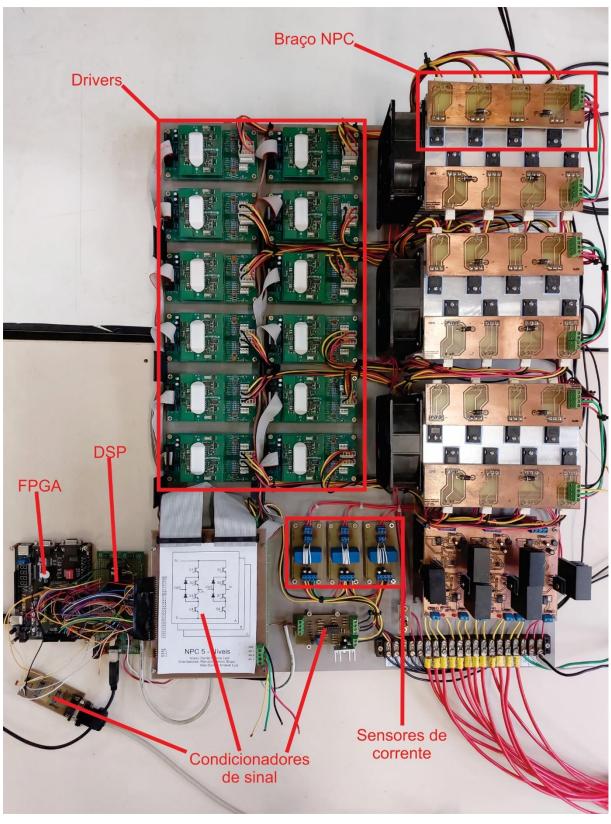

| Figura 38 – Diagrama completo do $\mathit{hardware}$ do acionamento da máquina de 2 $\mathit{cv}$ . 68 |

| Figura 39 – Foto da montagem do inversor NPC Tipo G69                                                  |

| Figura 40 – Circuito de entrada e barramento c.c70                                                     |

| Figura 41 – Tensão da fase a, tensão de linha $V_{ab}$ e corrente no motor de 2 ${\it CV}$ em          |

| regime permanente a vazio71                                                                            |

| Figura 42 – Espectro de frequência da tensão da fase a, tensão de linha Vab e da                       |

| corrente no motor de 2 CV em regime permanente a vazio72                                               |

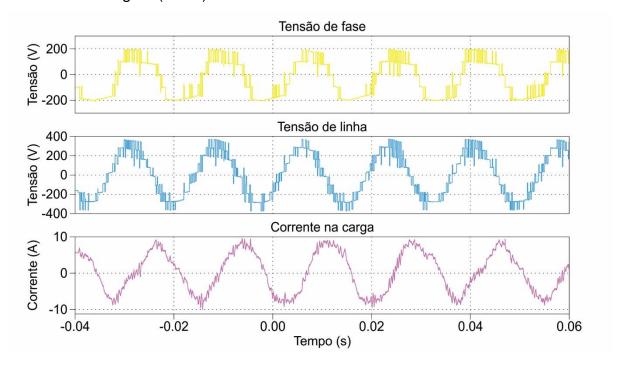

| Figura 43 – Tensão da fase a, tensão de linha V <sub>ab</sub> e corrente na carga no acionamento       |

| do motor de 2 CV em regime permanente a vazio com baixa taxa de amostragem                             |

| (5 <i>kHz</i> )73                                                                                      |

| Figura 44 – Tensão da fase a, tensão de linha Vab e corrente no motor de 2 CV em                       |

| regime permanente com conjugado estimado de 2,6 Nm74                                                   |

|                                                                                                        |

| Figura 45 – Espectro de frequência da tensão da fase a, da tensão de linha Vab e da     |

|-----------------------------------------------------------------------------------------|

| corrente no motor de 2 CV em regime permanente e conjugado estimado de 2,6 Nm.          |

| 74                                                                                      |

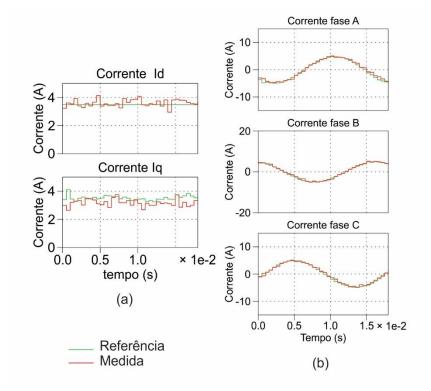

| Figura 46 – (a) Componentes de corrente em eixo direto $I_d$ e eixo quadradura $I_q$ de |

| referência e medidas e (b) correntes das fases a, b e c de referência e medidas, para   |

| o acionamento em regime permanente e com carga estimada de 2,6 $\mathit{Nm}$ 76         |

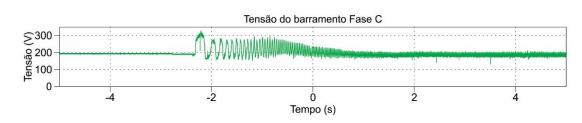

| Figura 47 – Tensão no barramento c.c. da Fase C77                                       |

| Figura 48 – Velocidade do rotor durante acionamento da máquina com reversão77           |

| Figura 49 – Foto dos motores utilizados no acionamento85                                |

| Figura 50 – Transformador utilizado na montagem do acionamento86                        |

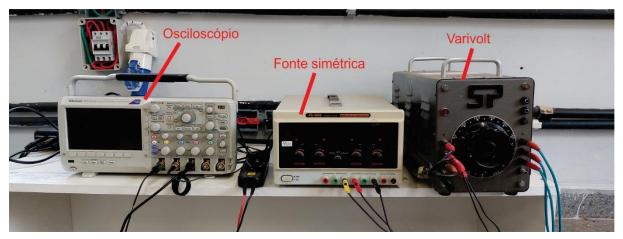

| Figura 51 – Parte superior da bancada com osciloscópio, fonte simétrica e varivolt.86   |

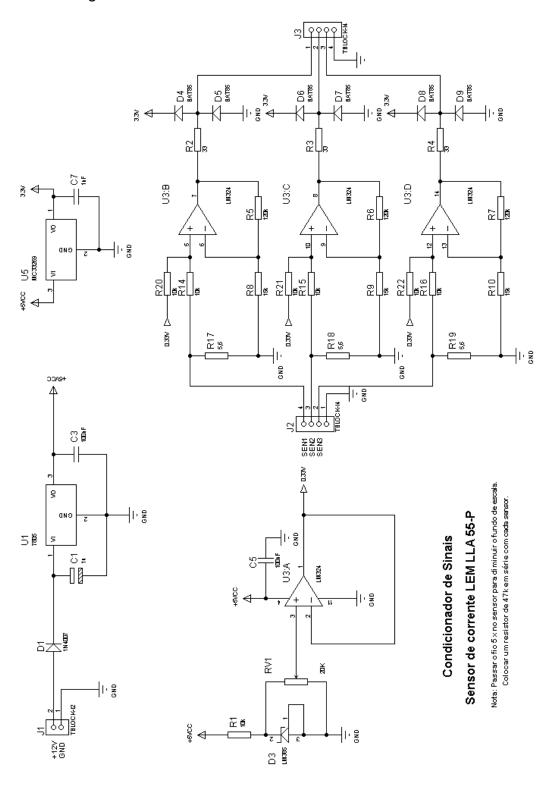

| Figura 52 – Diagrama do condicionador de sinais dos sensores de corrente87              |

| Figura 53 – Diagrama do condicionador de sinais do encoder de posição do motor.         |

| 88                                                                                      |

| Figura 54 – Diagrama do condicionador de sinais do DSP. Representação do circuito       |

| para um sinal89                                                                         |

# **LISTA DE TABELAS**

| Tabela 1 – Parâmetros da máquina de indução trifásica de 6.000 hp53                      |

|------------------------------------------------------------------------------------------|

| Tabela 2 – Distorção harmônica total (THD) para as tensões da fase a e de linha $V_{ab}$ |

| e corrente no motor para os acionamentos com frequência de amostragem de 5 e             |

| 20 kHz, com operação em regime permanente e plena carga                                  |

| Tabela 3 – THDs das tensões de fase, de linha e corrente na carga para os dois tipos     |

| de modutadores64                                                                         |

| Tabela 4 – Dados da máquina de indução trifásica de 2 cv                                 |

| Tabela 5 – Dados da máquina utilizada como emulador de cargas mecânicas67                |

| Tabela 6 - THDs das tensões de fase, de linha e corrente na carga para os                |

| acionamentos a vazio e com carga75                                                       |

# LISTA DE ABREVIATURAS E SIGLAS

c.a. Corrente alternada

THD Total Harmonic Distortion

NPC Neutral Point Clamped

CSI Current Source Inverter

VSI Voltage Source Inverter

PWM Pulse Width Modulation

c.c. Corrente Contínua

D-STATCOM Distribution Static Synchronous Compensator

CESP Current Error Space Vector

PD Phase Disposition

POD Phase Opposition Disposition

APOD Alternate Phase Opposition Disposition

PSC Phase Shift Carrier

CO Carrier Over lopped

DSP Digital Signal Processor

PI Proporcional Integral

FPGA Field Programable Gate Array

SVPD-PWM Space Vector Phase Disposition Pulse Width Modulation

GTO Gate Turn Off

IGBT Insulated-gate Bipolar Transistor

# **LISTA DE SÍMBOLOS**

*i*<sub>s</sub> Corrente de estator

*V<sub>DC</sub>* Fonte de tensão contínua

$f_c$  Frequência de comutação

*e*<sub>s</sub> Força contraeletromotriz

$r_s$  Resistência de estator

$L_s'$  Indutância transitória do estator

$p \frac{d}{dt}$

$\lambda_s$  Enlace de fluxo de estator

$\lambda_r$  Enlace de fluxo de rotor

$L_m$  Indutância mútua

*L<sub>s</sub>* Indutância própria de estator

$L_r$  Indutância própria de rotor

T<sub>e</sub> Conjugado eletromagnético

$\omega$  Velocidade angular

A/D Analógico/Digital

$T_L$  Conjugado da carga

j Unidade imaginária

Momento de inércia

P Número de pólos

Subscrito

d Eixo direto

q Eixo em quadratura

Sobrescrito

\* Valor de referência

*e* eixos com referencial rotativo

Valor estimado

# SUMÁRIO

| 1 INTRODUÇÃO                                                  | 17     |

|---------------------------------------------------------------|--------|

| 1.1 Controle de corrente                                      | 18     |

| 1.1.1 Histerese de corrente                                   | 20     |

| 1.2 Estudos recentes                                          | 23     |

| 1.3 Objetivos                                                 | 26     |

| 1.4 Contribuições                                             | 26     |

| 1.5 Estrutura do texto                                        | 27     |

| 2 CONVERSOR MULTINÍVEL E A TÉCNICA DE CONTROLE DO ACION<br>28 | AMENTO |

| 2.1 Topologia NPC                                             | 29     |

| 2.1.1 NPC Tipo G                                              | 32     |

| 2.2 Controle vetorial por orientação de campo do rotor        | 35     |

| 2.2.1 Controlador e sintonia                                  | 40     |

| 2.3 Conclusão                                                 | 42     |

| 3 CONTROLE POR HISTERESE DE CORRENTE MULTIFAIXA               | 43     |

| 3.1 Histerese multifaixa digital                              | 47     |

| 3.2 Circuito limitador de frequência                          | 49     |

| 3.3 Conclusão                                                 | 51     |

| 4 RESULTADOS DE SIMULAÇÃO E EXPERIMENTAIS                     | 52     |

| 4.1 Resultados de simulação para um acionamento de 6.000 hp   | 52     |

| 4.1.1 Parâmetros do acionamento                               | 52     |

| 4.1.2 Resultados de simulação                                 | 53     |

| 4.1.3 Comparação entre histerese multifaixa e SVPD-PWM        | 62     |

| 4.2 Resultados experimentais para um acionamento de 2 cv      | 65     |

| 4.2.1 Parâmetros do acionamento                               | 65     |

| 4.2.2 Descrição da bancada de testes                          | 66     |

| 4.2.3 Resultados experimentais                       | 71 |

|------------------------------------------------------|----|

| 4.2.3.1 Operação a vazio                             | 71 |

| 4.2.3.2 Operação com carga                           | 73 |

| 4.2.3.3 Operação transitória                         | 77 |

| 4.3 Conclusão                                        | 77 |

| 5 CONCLUSÕES                                         | 79 |

| 5.1 Propostas para trabalhos futuros                 | 80 |

| REFERÊNCIAS                                          | 81 |

| APENDICE A – FOTOS ADICIONAIS DA MONTAGEM            | 85 |

| APENDICE B – DIAGRAMAS DOS CONDICIONADORES DE SINAIS | 87 |

|                                                      |    |

# 1 INTRODUÇÃO

À medida que a automação industrial atinge um novo patamar em seu desenvolvimento, a tecnologia de acionamento de motores c.a. deve acompanhar essa evolução, uma vez que esse setor exige um controle flexível, permitindo o ajuste preciso de velocidade, aceleração e conjugado (NOVOTNY e LIPO, 1996). Em aplicações de alta potência, os acionamentos c.a. devem fornecer formas de onda de tensão e de corrente o mais senoidal possível em sua saída, o que pode ser obtido adicionando-se grandes filtros LC ou por meio de técnicas de comutação, além do aumento do número de níveis da tensão sintetizada. O uso de métodos adequados de comutação pode proporcionar economia de espaço e de recursos financeiros com esses filtros (RASHID, 2014). Nesse contexto, os conversores eletrônicos de potência necessitam de estratégias de modulação capazes de otimizar parâmetros como a frequência de comutação, a distorção harmônica, as perdas e a velocidade de resposta (LIPO, HOLMES e HOLMES, 2003). Além disso, o controle do acionamento de motores elétricos deve atender o comportamento da carga, fornecendo o conjugado mecânico demandado por ela em velocidades que podem variar ao longo do tempo, além de causar a menor perturbação possível ao sistema de fornecimento de energia elétrica. O contínuo avanço na tecnologia dos dispositivos semicondutores de potência tem permitido o desenvolvimento de drives c.a. que atendam essas necessidades, porém, como consequência, há um aumento na complexidade dos circuitos de comando dos interruptores eletrônicos.

As várias estratégias de modulação tendem a utilizar frequências de comutação elevadas. Porém, em aplicações de média tensão e alta potência, existem restrições para comutar em altas frequências, devido, principalmente, às perdas e à própria limitação nas características dos dispositivos empregados. Assim, como estratégia para minimizar esses efeitos, adota-se um aumento do número de níveis de tensão na operação dos inversores, cujo objetivo é dividir os esforços de cada interruptor eletrônico, além de diminuir a distorção harmônica total (THD) na forma de onda de tensão de saída do conversor (RASHID, 2014). Assim sendo, esse trabalho utilizará a topologia apresentada por (HILL e HARBOURT, 1999), o conversor NPC tipo G de 5 níveis, que além de multinível, possibilita a utilização de várias técnicas de comutação.

Naturalmente, diferentes estratégias de controle de comutação levam a diferentes resultados em termos de desempenho do conversor. O controle por faixa de histerese de corrente proposto neste trabalho atua na lógica de comutação fazendo com que a corrente na carga se aproxime de uma corrente de referência previamente estabelecida. A largura da faixa de histerese influencia diretamente na frequência de comutação e, consequentemente, na qualidade das ondas de tensão sintetizadas e na eficiência do inversor. Apesar de essa ser uma técnica simples, sua aplicação em inversores com topologias multinível aumenta consideravelmente a complexidade da implementação do comando dos interruptores eletrônicos (GAWANDE e RAMTEKE, 2014).

Mesmo com todo o estudo desenvolvido durante décadas, ainda há espaço para contribuição, como é proposto neste trabalho, através da aplicação do controle por histerese aplicado a um conversor multinível, na expectativa de melhorar a qualidade da tensão e corrente de saída sintetizadas no conversor, em conjunto com uma topologia que permite lidar com o acionamento em alta potência.

# 1.1 Controle de corrente

Acionamentos de alto desempenho utilizam estratégias de controle que fornecem sinais de comando para sintetizar as correntes das máquinas c.a., ou seja, são inversores regulados por corrente. A razão para a escolha da corrente como variável de controle é que alguns fatores dinâmicos como, efeitos de resistência, indutância e força contra eletromotriz são eliminados. Inversores do tipo fonte de corrente (CSIs) e fonte de tensão (VSIs) com modulação por largura de pulso (PWM) podem operar em modo de controle de corrente. O CSI pode ser mais prontamente colocado em operação com o controle de corrente, porém, o VSI apresenta maior largura de faixa e eliminação de harmônicos na forma de onda da corrente (NOVOTNY e LIPO, 1996) além de possuírem um custo consideravelmente menor em sua produção.

Os VSIs têm sido amplamente pesquisados, em especial as topologias multiníveis, na tentativa de operar com altas faixas de potência e baixa distorção harmônica. Dentre os muitos tipos de inversores multinível, o *Neutral-Point-Clamped* (NPC) com comando PWM é bem conhecido por tornar o conversor bem eficiente,

tanto em meia-ponte quanto em ponte-completa, além de permitir o emprego de várias técnicas de modulação.

O desempenho dos conversores depende muito da estratégia de controle de corrente aplicada. Em comparação com conversores PWM convencionais, o conversor PWM controlado por corrente tem as seguintes vantagens (KAZMIERKOWSKI e MALESANI, 1998):

- controle da forma de onda da corrente instantânea e alta precisão;

- rejeição de sobrecarga;

- excelente dinâmica;

- proteção contra sobrecorrente e curto circuito;

- compensação de efeitos causados por mudança de parâmetros da carga (resistência e reatância);

- compensação de queda de tensão dos semicondutores e do tempo morto do conversor:

- compensação de alterações na tensão do barramento c.c.

- rejeição de perturbação.

A precisão de um controle de corrente pode ser avaliada de acordo com alguns requisitos básicos:

- ausência de erros de fase e amplitude em uma larga faixa de frequência de saída;

- rápida resposta dinâmica do sistema;

- baixo conteúdo harmônico;

- boa utilização do barramento c.c.

As técnicas de controle de corrente para VSIs podem ser categorizadas como lineares e não-lineares. Os controladores de corrente lineares são caracterizados por possuírem uma frequência de comutação fixa, porém, com algumas limitações de desempenho. Um controlador não-linear pode ser baseado em estratégias de histerese, que por sua vez possui a desvantagem de apresentar uma frequência de comutação variável (NOVOTNY e LIPO, 1996), mas oferecem uma rápida resposta a eventos transitórios (BODE e HOLMES, 2000); (JENA, CHITTI BABU e SAMANTARAY AND M. MOHAPATRA, 2011). Outra vantagem do regulador por histerese de corrente é que ele utiliza diretamente as referências de corrente para sintetizar a tensão de saída do conversor, dispensando o uso de desacopladores de tensão, necessários no caso dos controladores de corrente lineares. Esse

desacoplador de tensão transforma as referências de corrente em referências de tensão, e depende ainda mais de uma estimativa precisa dos parâmetros da máquina para que não ocorram erros no controle por orientação de campo.

# 1.1.1 Histerese de corrente

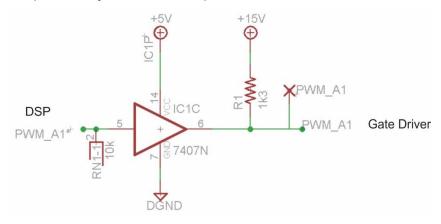

Dentre os métodos de controle de corrente não-lineares, o controle por histerese é o tipo mais simples de ser implementado. A Figura 1(a) mostra um conversor de dois níveis meia ponte trabalhando como um inversor monofásico com uma carga RL conectada nos terminais de saída U-N. Os interruptores eletrônicos  $S_1$  e  $S_2$  aplicam as tensões  $V_{DC}$  e  $-V_{DC}$  na carga, respectivamente, e não devem ser acionados simultaneamente para evitar um curto circuito no barramento c.c. O controlador da Figura 1(b) simplesmente aplica o sinal de erro da corrente em um elemento de histerese, e sua saída fornece o sinal lógico para o acionamento dos interruptores eletrônicos.

Figura 1 – (a) Conversor meia ponte de dois níveis trabalhando como inversor monofásico e (b) seu circuito de comando com histerese de corrente.

Fonte: Elaborado pelo autor, 2023.

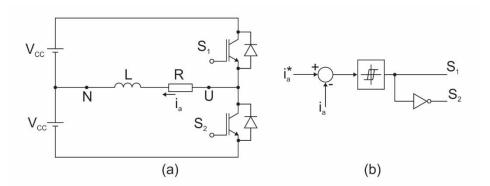

A Figura 2(a) mostra o comportamento das formas de onda de tensão e corrente sintetizadas na saída do inversor monofásico de dois níveis da Figura 1(a) comandado por histerese de corrente. Para uma dada referência de corrente  $i_a^*$ , são definidas as faixas de histerese superior e inferior. No momento  $t_1$ , a corrente na carga  $i_a$  está diminuindo, se afastando de  $i_a^*$ , quando atinge a faixa de histerese inferior. Nesse momento, o interruptor  $S_1$  é acionado e o interruptor  $S_2$  é desligado, sendo

aplicada uma tensão  $V_{cc}$  na carga RL. Esse comando provoca a mudança no sentido de  $i_a$ , que vai novamente em direção a  $i_a^*$ . Em  $t_2$  a corrente na carga  $i_a$ , que estava novamente se afastando de  $i_a^*$ , atinge a faixa de histerese superior, e o circuito de comando ativa o inturruptor  $S_2$  e desliga o interruptor  $S_1$ , fazendo com que seja aplicada uma tensão  $-V_{cc}$  na carga RL, corrigindo a trajetória de  $i_a$  em direção a  $i_a^*$ . Esse ciclo, então, se repete constantemente, com o objetivo de que  $i_a$  se aproxime sempre de  $i_a^*$ .

Figura 2 – (a) Comportamento das formas de onda de tensão e corrente sintetizadas na saída do inversor monofásico comandado por histerese de corrente e (b) o sinal de erro da corrente aplicado no elemento de histerese.

Fonte: Elaborado pelo autor, 2023.

A grande desvantagem do controle por histerese de corrente é a frequência de comutação variável, podendo causar o aparecimento de componentes de baixa frequência no espectro harmônico da corrente. Além disso, altas frequências de comutação podem exceder o limite dos dispositivos semicondutores, principalmente aqueles destinados a operar em altas faixas de potência.

Na Figura 2(b), a trajetória completa de subida e descida do erro de corrente entre as faixas de histerese representa uma oscilação de frequência  $f_c$ , que é a frequência de comutação do inversor. NOVOTNY e LIPO, (1996), apresentam uma forma de estimar a  $f_c$  máxima em um inversor de dois níveis trifásico comandado por histerese de corrente acionando um motor de indução. Em geral, a equação vetorial

da máquina de indução que relaciona a tensão de estator  $\vec{v_s}$ , a corrente de estator  $\vec{l_s}$  e força contraeletromotriz  $\vec{e_s}$  é dada por

$$\overrightarrow{v_s} = r_s i_s + L_s' p \overrightarrow{i_s} + \overrightarrow{e_s} \tag{1}$$

onde  $r_s$  e  $L_s'$  são a resistência de estator e a indutância transitória do estator, respectivamente e p é o operador de derivada. A frequência de comutação é maior quando o maior valor de tensão é aplicado no estator (maior inclinação da corrente), ou seja, quando  $\overrightarrow{e_s}$  é pequeno. Desconsideranto  $r_s$ , a Equação 1 se torna

$$\overrightarrow{v_s} = L_s' p \overrightarrow{l_s} \tag{2}$$

A estimativa de  $f_c$  máxima é feita dividindo-se a velocidade da trajetória da corrente pela distância percorrida em um período completo de um ciclo. Para uma força contraeletromotriz igual a zero, a velocidade em amperes por segundo é aproximadamente

$$velocidade = \frac{di_s}{dt} \approx \frac{2}{3} \frac{V_{DC}}{L_s'}$$

, (3)

onde  $L_s'$  é a indutância transitória do estator da máquina.

Como o inversor é trifásico e a comutação de cada fase influencia nas outras, a distância em amperes percorrida em um ciclo completo do erro de corrente é

$$distancia = \Delta i_s \approx 6h$$

(4)

onde h é a largura da faixa de histerese.

A frequência de comutação máxima do inversor é dada, então, como

$$f_c = \frac{velocidade}{distância} = \frac{V_{DC}}{9hL_S'}$$

(5)

A seção seguinte apresenta alguns dos estudos recentes envolvendo a técnica da histerese de corrente aplicada em diversas áreas.

### 1.2 Estudos recentes

Algumas características interessantes dos reguladores por histerese de corrente, como a resposta dinâmica, rápida resposta de corrente e a baixa dependência dos parâmetros da carga, têm renovado o interesse pelo uso dessa técnica em várias áreas como geração distribuída, compensadores estáticos de potência e acionamento de motores.

SINGH e BEHERA (2018) fazem um estudo de controladores por histerese de corrente em inversores conectados à rede, com aplicação na área de geração distribuída, revisando os conceitos das histereses de faixa simples, faixa dupla e faixa variável. Através de resultados de simulações e experimentais, o artigo mostra que o melhor nível de THD é obtido utilizando-se a técnica de faixa dupla de histerese, que, nesse caso, produz uma forma de onda de tensão na saída do inversor com três níveis. Neste caso, a mesma técnica não pode ser usada em conversores com mais de três níveis. Além disso, o trabalho lista o resultado da análise das técnicas com a frequência máxima de comutação, porém não evidencia a estratégia utilizada para garantir esse limite.

RAJASEKHAR e RAMADEVI (2018) apresentam um D-STATCOM (*Distribution Static Synchronous Compensator*) que utiliza a técnica de modulação por histerese de corrente multifaixa, aplicada a um conversor multinível em cascata. Neste caso, o conversor aproveita as características da modulação por histerese para mostrar as vantagens em relação às técnicas tradicionais. Neste trabalho é utilizado um método para a estimativa da faixa de frequência de comutação para uma dada faixa de histerese, sendo possível indicar as frequências mínima, máxima e média. Porém, nenhuma ação é tomada com o propósito de limitar efetivamente a frequência de comutação.

SRIKAR, et al., (2018), fazem uma comparação entre duas técnicas de modulação por histerese de corrente. A primeira técnica é baseada no fasor espacial do erro de corrente (*Current Error Space Phasor* - CESP), na qual a cada período de amostragem o inversor comuta a saída de tensão de modo a manter o sinal de corrente, em referencial  $\alpha\beta$ , dentro de um padrão particular. Para calcular esse padrão

do erro de corrente, as tensões fundamentais de estator precisam ser estimadas para, então, a partir disso, determinar os três vetores de tensão mais próximos. A segunda estratégia utiliza o valor médio das tensões do inversor para gerar faixas de histerese variáveis de modo que o erro de corrente oscile, e desse modo a frequência de comutação é quase constante. Ambas as técnicas são aplicadas com sucesso a um inversor de dois níveis para acionamento de um motor de indução, porém, não se pode concluir que as mesmas técnicas possam ser diretamente aplicadas em inversores multinível. Parte dessa lacuna é preenchida no trabalho de RAJU, et al., (2019), que aplica a mesma técnica CESP a um conversor ponte-H em cascata de três níveis utilizado como um STATCOM. Porém, neste caso, o trabalho apresenta implementação apenas através de simulação, sem levar em conta possíveis efeitos na discretização do sistema e possíveis especificidades na implementação via hardware.

O trabalho apresentado por PATIL, et al., (2018), tem uma proposta bem alinhada com este. Os autores fazem uma comparação entre técnicas de PWM lineares e a histerese de corrente, aplicadas a conversores multinível. As técnicas analisadas são a *phase disposition* (PD), *phase opposition disposition* (POD), alternate phase opposition disposition (APOD), phase shift carrier (PSC), carrier overlapped (CO) e histerese de corrente. Apesar da proposta interessante, a comparação entre as técnicas de modulação é feita apenas levando em consideração características teóricas, e fica devendo dados quantitativos e resultados experimentais que confirmem as afirmações.

Além do uso em acionamento de motores, a técnica de modulação por histerese de corrente também tem sido aplicada em compensadores estáticos, como é o caso do trabalho de LINCA, et al., (2018). Neste trabalho é apresentada uma técnica de modulação por controle de histerese de corrente com frequência de comutação constante. Para isso, o sinal de erro de corrente da histerese clássica é sobre-modulado com o sinal de uma portadora triangular, antes de ser aplicado aos elementos de histerese. A frequência de comutação, nesse caso, se torna constante e igual à frequência da portadora. Porém, como relatado pelos próprios autores, para garantir a operação apropriada, a frequência de comutação (portadora) deve ser alta, dificultando sua aplicação em sistemas de alta potência e com portadoras sintetizadas digitalmente por Processadores de Sinais Digitais (DSPs).

Também existem propostas de melhorar técnicas já existentes, como no caso do artigo de STOJIć, et al., (2019) que propõe uma modificação no controlador por histerese de corrente baseado em eixo com referencial síncrono. Aqui ele obtém um controle de corrente robusto, associado a um erro nulo em operação em regime permanente. Porém, o artigo não contempla a discussão da característica própria da modulação por histerese de corrente que é a frequência de comutação variável, que neste caso, pode chegar a valores altos e inaceitáveis.

No trabalho de YALLA, et al., (2020), o controle por histerese de corrente é aplicado a um conversor c.a.-c.c. com alto fator de potência. O conversor é multinível, e sua construção utiliza a topologia de grampeamento em múltiplos pontos. Neste artigo, a histerese de corrente multifaixa é comparada com um novo método proposto, que utiliza apenas uma faixa de histerese e se baseia em tempo para seleção dos níveis de tensão do conversor. A associação da topologia com o método de histerese proposto apresenta algumas vantagens sobre a técnica multifaixa, porém, parte do acionamento é implementado de forma analógica, o que deixa uma margem para discussão, já que sistemas modernos tendem a ser implementados de forma digital. Também não há no artigo uma discussão sobre a questão da frequência de comutação variável, própria dos controladores por histerese de corrente.

LAKSHMI e MATHEW (2022) apresentam um método de histerese de corrente com frequência de comutação constante. Nesta técnica, não é necessária uma faixa de histerese. A ação de controle da histerese é determinada por um comparador ou pelo tempo de inclinação da corrente. Neste caso, a técnica é aplicada a um inversor de dois níveis trifásico conectado à rede, e não pode ser aplicada diretamente a conversores multinível.

Por fim, o estudo recente de SURU, et al., (2023) apresenta uma proposta muito semelhante à deste trabalho, sugerindo, justamente, limitar a frequência de comutação do modulador controlado por histerese de corrente, utilizado no acionamento de um motor controlado por orientação de campo do rotor, e aplicado a um inversor de dois níveis. Neste caso, o método consiste em ajustar a faixa de histerese a cada período de amostragem, regulando a frequência de comutação, através de um controlador do tipo proporcinal-integral (PI). A principal diferença é que, a limitação da frequência de comutação, neste caso, depende da dinâmica do controle PI. Outra questão a ser analisada é se a mesma técnica poderia ser aplicada a um conversor multinível.

# 1.3 Objetivos

O objetivo principal deste trabalho é avaliar a operação e o desempenho da técnica de controle de corrente por histerese em um conversor NPC de cinco níveis tipo G, com limitação da frequência de comutação. Para isso, é feito um estudo baseado em simulação e experimentação em laboratório, com o desenvolvimento de um protótipo.

O estudo baseado em simulação tem como objetivo uma análise prévia dos métodos, utilizando parâmetros que não foram possíveis de serem implementados em laboratório, neste trabalho.

O estudo baseado em experimentação objetiva validar os resultados obtidos por simulação e avaliar as especificidades da implementação do acionamento em uma situação real, mesmo que em escala reduzida.

Um dos desafios desse trabalho é fazer com que a técnica de histerese de corrente trabalhe com frequência de comutação limitada.

# 1.4 Contribuições

A principal contribuição deste trabalho é o desenvolvimento, implementação e avaliação experimental de uma estratégia de limitação da frequência de comutação de um controlador de histerese digital para um conversor de cinco níveis Tipo G, além do estudo dos efeitos da discretização do controle de corrente na sua implementação digital através do uso de um dispositivo DSP combinado com um FPGA, aplicado a acionamentos de média tensão e alta potência. Este estudo mostra que a eficácia do método de histerese de corrente multifaixa depende da frequência de amostragem, e propõe a dissociação entre a frequência de amostragem e frequência de atuação do conversor.

Outra contribuição importante é o estudo dos efeitos da discretização do acionamento, uma vez que a proposta é de implementação digital do controle, como é feito nos conversores comerciais atuais.

Neste sentido, o trabalho intitulado "A New Limited Switching Frequency Digital Hysteresis Current Control Strategy for a Five-Level Medium Voltage Induction Motor Drive" foi apresentado no XXIV Congresso Brasileiro de Automática, em outubro de

2022, em Fortaleza, Ceará. O artigo mostra o controle por histerese de corrente multifaixa digital com um circuito limitador de frequência aplicado no acionamento de uma máquina de indução e compara os resultados com a técnica convencional que limita a frequência de comutação através da taxa de amostragem.

Outro desdobramento deste estudo é o artigo intitulado "A Comparative Study of SVPD-PWM and Multiband hysteresis Through Digital Implementation for a Type-G Converter", a ser apresentado na 70ª annual conference of Petroleum and Chemical Industry Committe (PCIC), em New Orleans, EUA. O trabalho faz uma comparação da metodologia proposta com uma técnica de modulação já consolidada e usada comercialmente que é a SVPD-PWM.

### 1.5 Estrutura do texto

O texto está organizado de acordo com a seguinte estrutura:

Capítulo 1: introdução do tema proposto, mostrando a relevância e os objetivos pretendidos com este estudo.

Capítulo 2: apresenta a teoria básica da topologia do conversor multinível utilizado, além da técnica de controle para a geração das correntes de referência que são utilizadas pela modulação por histerese de corrente.

Capítulo 3: Apresenta a técnica de modulação por histerese de corrente multifaixa, apontando a dificuldade de sua implementação digital e propondo uma solução para superar este problema.

Capítulo 4: detalha a implementação do acionamento através de simulação e implementação de protótipo em laboratório. Os resultados são apresentados e discutidos.

Capítulo 5: apresenta o fechamento do texto, com a conclusão do trabalho e sugestões para estudos futuros.

# 2 CONVERSOR MULTINÍVEL E A TÉCNICA DE CONTROLE DO ACIONAMENTO

Inversores que trabalham na faixa de média tensão possuem um problema comum para operar em altas frequências de comutação que são as limitações dos dispositivos semicondutores de alta potência. A frequência de comutação se refere ao número de vezes que o interruptor eletrônico comuta em um segundo. Toda vez que um interruptor liga ou desliga é gerada uma perda, e desse modo, quanto maior é a frequência de comutação, maior serão as perdas. Essas perdas estão diretamente ligadas à tensão de barramento e à corrente através do interruptor, desse modo, em um conversor de alta potência as perdas associadas à comutação podem elevar muito a temperatura de um interruptor levando-o ao colapso. Além disso, estes dispositivos muitas vezes são incapazes de operar com altas taxas de variação de tensão (dv/dt) e bloquear altos níveis de tensão. Uma maneira de contornar essas limitações é utilizar inversores com topologia multinível, que dividem o esforço desses semicondutores ao bloquear a tensão e permitem trabalhar com sistemas de alta potência, além de melhorar a THD das formas de onda sintetizadas sem necessariamente aumentar a frequência de comutação (LEAL, LUIZ e STOPA, 2022).

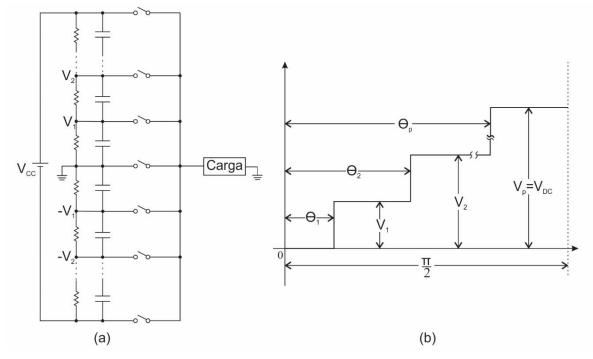

A Figura 3 mostra um conceito simples de um inversor multinível meia-ponte. O barramento c.c. é composto por uma fonte de tensão  $V_{CC}$  e divisores que produzem vários níveis de tensão intermediários. Cada interruptor é acionado em um ângulo  $\theta$  diferente, variando a tensão na carga entre os vários níveis disponíveis no barramento c.c., produzindo uma forma de onda de saída em degraus que possibilita a diminuição de componentes harmônicas de baixa frequência (BHAGWAT e STEFANOVIC, 1983).

Figura 3 – (a) Esquema de um inversor multinível meia-ponte e (b) forma de onda típica da tensão de saída em degraus.

Fonte: (BHAGWAT e STEFANOVIC, 1983).

Apesar de melhorar a qualidade da forma de onda de tensão na saída do inversor, a topologia apresentada na Figura 3 ainda exige que os interruptores bloqueiem a tensão total do barramento. Desse modo, para aplicações de alta potência seria necessário, por exemplo, o uso de tiristores do tipo GTO (gate turn off), que conseguem operar com faixas de média tensão de bloqueio, porém, com velocidade de comutação limitada se comparados com os IGBTs (insulated-gate bipolar transistor). Assim, existem várias topologias de conversores multiníveis que utilizam diferentes estratégias para lidar com as altas tensões de bloqueio. Uma delas é a topologia neutral-point-clamped (NPC), bastante consolidada e utilizada amplamente comercialmente, e que está descrita na seção seguinte.

# 2.1 Topologia NPC

Uma topologia de inversor muito importante em aplicações de alta potência é o NPC (NABAE, TAKAHASHI e AKAGI, 1981). A Figura 4 mostra o circuito do inversor de 3 níveis NPC. O 0 indica o ponto neutro em relação ao barramento c.c., os interruptores eletrônicos  $S_{11}$ ,  $S_{14}$ ,  $S_{21}$ ,  $S_{24}$ ,  $S_{31}$  e  $S_{34}$  são os principais para a operação

do PWM.  $S_{12}$ ,  $S_{13}$ ,  $S_{22}$ ,  $S_{23}$ ,  $S_{32}$  e  $S_{33}$  são os interruptores auxiliares que grampeiam os terminais de saída no potencial do ponto neutro juntamente com os diodos  $D_{11}$  -  $D_{32}$ .

Figura 4 – Inversor de 3 níveis tipo NPC.

Fonte: (NABAE, TAKAHASHI e AKAGI, 1981).

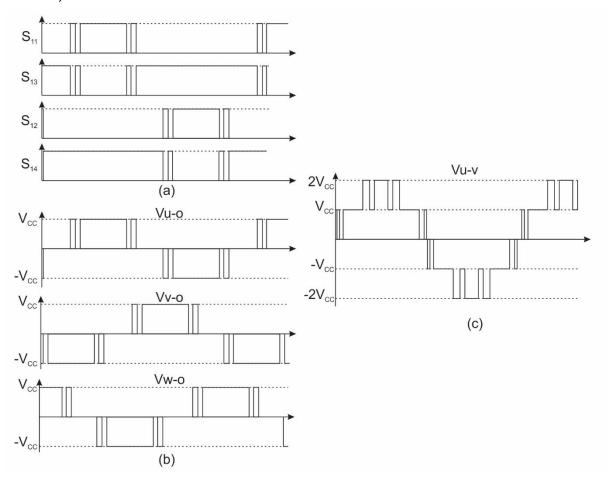

Os interruptores eletrônicos auxiliares  $S_{12}$  e  $S_{13}$  são complementares de  $S_{14}$  e  $S_{11}$ , respectivamente. A Figura 5(a) mostra o detalhe dos sinais de comando do braço da fase U do inversor NPC de 3 níveis. Quando há o comando para desligar os interruptores principais vindo do modulador PWM, a tensão no terminal de saída é grampeada no potencial do ponto neutro, como é mostrado na Figura 5(b). A Figura 5(c) mostra a forma de onda de tensão entre os terminais de saída u-v do inversor (tensão de linha), que nesse caso fornecem 5 níveis de tensão.

Além de apresentar um melhor conteúdo harmônico nas formas de onda de saída em comparação a um inversor convencional de dois níveis, no NPC cada interruptor eletrônico bloqueia apenas metade da tensão do barramento. Isso permite que o inversor possa lidar com tensões e potências maiores. Em compensação, o conversor NPC necessita do dobro do número de interruptores, além dos diodos adicionais. Outro problema, que não ocorre em inversores de dois níveis, é a necessidade de garantir o balanceamento das tensões dos dois capacitores em série que fazem parte do barramento c.c. Uma solução é conectar cada capacitor em sua própria fonte c.c. isolada (HOLMES e LIPO, 2003). Outro método é balancear a tensão nos capacitores através de controle por realimentação como proposto em (SHUKLA, GHOSH e JOSHI, 2008) e (HATTI, HASEGAWA e AKAGI, 2009).

Figura 5 – (a) Sinais de comando dos interruptores eletrônicos do braço referente à fase U, (b) formas de onde de saída de tensão entre os terminais de saída e o ponto neutro e (c) tensão entre dois terminais de saída u-v do inversor NPC 3 níveis (tensão de linha).

Fonte: (NABAE, TAKAHASHI e AKAGI, 1981).

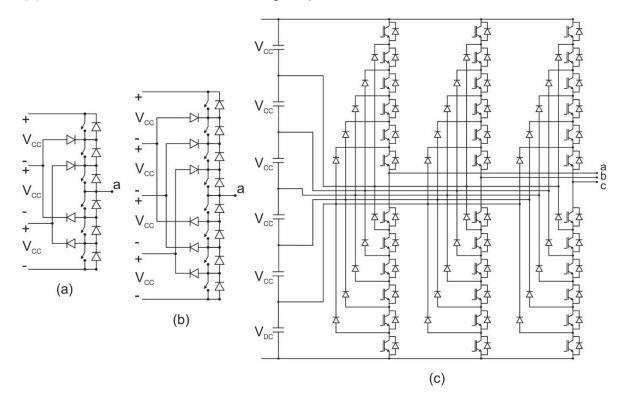

O princípio do grampeamento a diodos pode ser estendido para qualquer número de níveis de tensão utilizando-se vários capacitores conectados em série para subdividir o barramento c.c., conforme exemplificado na Figura 6 para os casos de quatro, cinco e sete níveis. Se N é o número de níveis de tensão do inversor com grampeamento a diodos, cada interruptor eletrônico deve bloquear uma tensão  $V_{CC}$ , porém, a tensão que cada diodo deve bloquear pode atingir  $V_{CC}(N-1)$ . Nesses casos, como são criados vários níveis de tensão intermediários, manter o balanceamento das tensões dos capacitores em série é um problema desafiador, já que o uso de fontes c.c. isoladas aumenta consideravelmente o custo dos equipamentos, sendo mais indicado o uso de algoritmos de controle apropriados.

Figura 6 – (a) Braço de um inversor a diodos de quatro níveis e (b) um de cinco níveis, e (c) um inversor de sete níveis com grampeamento a diodo.

Fonte: (HOLMES e LIPO, 2003).

A topologia NPC possui algumas variações, dentre elas a NPC Tipo G, que é descrita na seção seguinte.

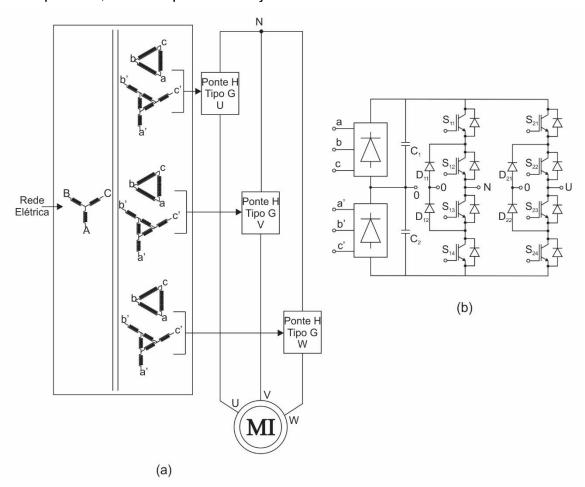

# 2.1.1 NPC Tipo G

O inversor NPC Tipo G foi apresentado pela primeira vez por HILL e HARBOURT, (1999), e produzido pela GE. A configuração do circuito de potência está representada na Figura 7(a), que mostra três pontes H conectadas em um ponto neutro comum. Cada ponte é alimentada por dois retificadores trifásicos isolados, que ajudam no balanceamento das tensões dos capacitores. A necessidade de transformadores especiais é uma desvantagem dessa topologia. O transformador Y-Δ estendido é utilizado para a redução do conteúdo harmônico na corrente de entrada dos retificadores.

Cada ponte H do inversor NPC é formada por dois braços idênticos aos utilizados no NPC de três níveis convencional, como mostra a Figura 7(b). Esta

topologia fornece cinco níveis de tensão de fase na saída do inversor, e nove níveis na tensão de linha, melhorando a THD.

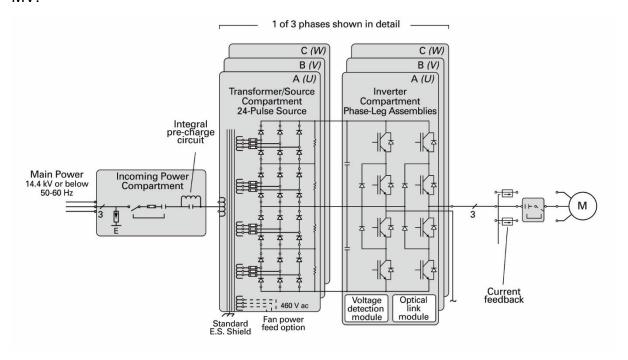

Essa topologia é utilizada comercialmente, como exemplo do inversor de frequência de média tensão modelo MVW01 do fabricante WEG, ilustrado na Figura 8. O MVW01 consegue lidar com motores com tensão nominal de 2,3 a 6,9 kV, e faixa de potência de 500 a 49.000 hp. A Toshiba também oferece um acionador de média tensão com topologia NPC Tipo G, o modelo Dura-Bilt5i MV, cujo esquema é apresentado na Figura 9. O Dura-Bilt5i MV opera motores de 2.300 a 4.160 V e potência de 200 a 10.000 hp.

Figura 7 – (a) Configuração do circuito de potência do inversor NPC Tipo G e (b) seu módulo ponte H, formado por dois braços de um inversor NPC três níveis.

Fonte: (LUIZ e STOPA, 2015).

Figura 8 – Inversor de frequência de média tensão modelo MVW01 da WEG.

Fonte: (WEG, 2023).

Figura 9 – Esquema do circuito de potência do inversor Toshiba modelo Dura-Bilt5i MV.

Fonte: (TMEIC, 2023).

O inversor NPC Tipo G pode ser comandado por várias técnicas de modulação, incluindo o controle por histerese de corrente, como é mostrado mais adiante neste trabalho.

# 2.2 Controle vetorial por orientação de campo do rotor

Para implementar o controle vetorial por orientação de campo do rotor, uma maneira muito útil e compacta de representar as equações da máquina de indução é através do uso da notação em variáveis complexas. Dessa forma, sua representação é feita por vetores espaciais com eixos de referência dq rotativos com velocidade  $\omega_e$ , sendo a tensão de estator  $\overrightarrow{v_s^e}$  e a tensão de rotor  $\overrightarrow{v_r^e}$  dadas por

$$\overrightarrow{v_S^e} = r_S \overrightarrow{l_S^e} + \frac{d}{dt} \overrightarrow{\lambda_S^e} + j\omega_e \overrightarrow{\lambda_S^e}$$

(6)

$$\overrightarrow{v_r^e} = r_r \overrightarrow{\iota_r^e} + \frac{d}{dt} \overrightarrow{\lambda_r^e} + j(\omega_e - \omega_r) \overrightarrow{\lambda_r^e}$$

(7)

onde

$$\overline{\lambda_S^e} = L_S \overline{\iota_S^e} + L_m \overline{\iota_r^e} \tag{8}$$

$$\overline{\lambda_r^e} = L_r \overline{\iota_r^e} + L_m \overline{\iota_s^e} \tag{9}$$

$L_m$ ,  $L_s$  e  $L_r$  são, respectivamente a indutância mútua, indutância própria de estator e indutância própria de rotor.  $r_s$  é a resistência de estator e  $r_r$  é a resistência de rotor. O conjugado é dado por

$$T_{e} = \frac{\frac{3}{2} \frac{P}{L_{m}}}{\frac{L_{m}}{L_{r}}} (\lambda_{dr}^{e} i_{qs}^{e} - \lambda_{qr}^{e} i_{ds}^{e})$$

(10)

Para possibilitar o controle direto da produção de conjugado, os eixos dq devem ser síncronos com o enlace de fluxo de rotor, ou seja,  $\omega_e$  deve ter a velocidade instantânea de  $\overrightarrow{\lambda_r}$ , e deve estar inteiramente em fase com o eixo d, resultando em

$$\lambda_q^e = 0 \tag{11}$$

Assumindo que o motor é alimentado em corrente, a equação vetorial de tensão de estator pode ser omitida, e, as equações com eixos síncronos com o vetor enlace de fluxo de rotor, decompostas nos eixos d e q são

$$0 = r_r i_{ar}^e + (\omega_e - \omega_r) \lambda_{dr}^e \tag{12}$$

$$0 = r_r i_{dr}^e + p \lambda_{dr}^e \tag{13}$$

$$\lambda_{qr}^e = L_m i_{qs}^e + L_r i_{qr}^e = 0 \tag{14}$$

$$\lambda_{dr}^{e} = L_{lr}i_{dr}^{e} + L_{m}(i_{ds}^{e} + i_{dr}^{e}) \tag{15}$$

$$T_e = \frac{3}{2} \frac{P}{L_r} \frac{L_m}{L_r} \left( \lambda_{dr}^e i_{qr}^e \right) \tag{16}$$

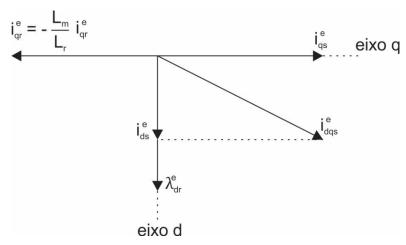

Nesse modelo, temos um "desacoplamento" nas equações da máquina. A componente de corrente de eixo em quadratura  $i_{qs}^e$  é responsável pelo comando direto de conjugado, enquanto a componente de eixo direto  $i_{ds}^e$  atua diretamente no fluxo do rotor, como pode ser percebido no diagrama fasorial da Figura 10.

Dada a dificuldade de se medir (ou calcular) o ângulo do vetor enlace de fluxo do rotor, o mais usual é a utilização do controle por orientação indireta de campo, que se baseia na relação de escorregamento da Equação 17, que é obtida a partir da Equação 12.

$$\omega_e - \omega_r = S\omega_e = -\frac{r_r i_{qr}^e}{\lambda_{dr}^e} \tag{17}$$

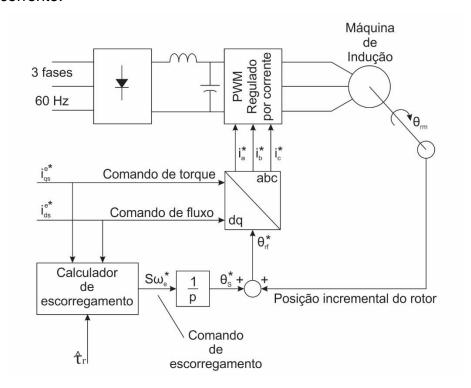

Se a relação de escorregamento é satisfeita, a componente de corrente do estator  $i_{ds}$  estará alinhada com o vetor enlace de fluxo do rotor. A Figura 11 ilustra a estrutura básica de um acionamento com controle por orientação indireta de campo utilizando comandos de corrente como entrada. A informação sobre a posição do rotor é obtida diretamente de um *encoder* acoplado ao eixo do motor. O ângulo do campo do rotor  $\theta_{rf}$  é determinado pela soma do sinal de posição do rotor e o sinal de posição do escorregamento.

Figura 10 – Componentes d e q das correntes do motor referencial rotativo síncrono como o fluxo do rotor.

Fonte: (NOVOTNY e LIPO, 1996).

Figura 11 - Sistema básico de orientação indireta de campo em máquina de indução usando um modulador PWM regulado por corrente.

Fonte: (NOVOTNY e LIPO, 1996).

Neste caso, para usar as variáveis  $i_{ds}^{e*}$  e  $i_{qs}^{e*}$  como entrada, a relação de escorregamento é dada pela Equação 18, obtida na associação das Equações 17, 14 e 15.

$$S\omega_e^* = \frac{\left(\frac{1}{\hat{\tau}_r}\right)i_{qs}^{e^*}}{\left(\frac{1}{1+p\hat{\tau}_r}\right)i_{ds}^{e^*}} \tag{18}$$

onde  $au_r = rac{L_r}{r_r}$  é constante de tempo rotórica.

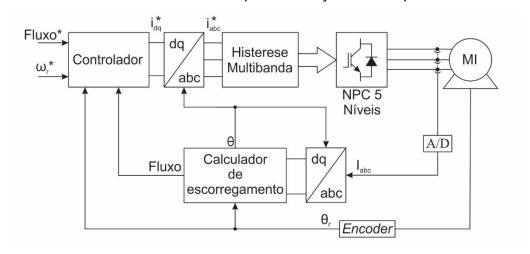

No acionamento proposto neste trabalho, a componente  $i_{ds}$  é obtida através de uma referência de fluxo de rotor, que neste caso é considerado constante. A componente  $i_{qs}$  é obtida através de uma malha de controle de velocidade. O diagrama do acionamento completo está representado na Figura 12, no qual o motor de indução é acionado por um inversor de 5 níveis NPC Tipo G, que por sua vez é comandado por um modulador do tipo histerese de corrente multifaixa. O controle é vetorial por orientação indireta de campo de rotor. Além da malha de velocidade, foi implementada ainda uma malha de controle para o fluxo, que é pouco usual, porém, reduz consideravelmente o tempo de execução da simulação. O controlador é detalhado na Seção 2.2.1.

Figura 12 - Diagrama completo do acionamento da máquina de indução por inversor NPC 5 níveis, comandado por histerese de corrente multifaixa e com controle vetorial por orientação de campo.

Conforme pode ser observado na Figura 12, o cálculo da relação de escorregamento depende das variáveis de corrente no motor que são medidas, e, no acionamento com implementação digital, são amostradas por um conversor analógico/digital (A/D). No processamento digital do controle existe um atraso inevitável nos comandos do conversor devido ao tempo de execução do programa. Este atraso, normalmente, é de um período de amostragem (tempo entre uma amostra e outra). No caso do controle de corrente com eixos síncronos, este atraso resulta no erro da estimativa do ângulo que causa um erro na amplitude e fase das correntes de saída. Assim, em acionamentos com frequência de amostragem baixa, o desempenho do conversor pode ser consideravelmente comprometida (BON-HO BAE e SUL, 2001). Então, os conversores devem manter uma alta razão entre a frequência de amostragem e a frequência de saída, ou possuir maneiras de compensar esse atraso.

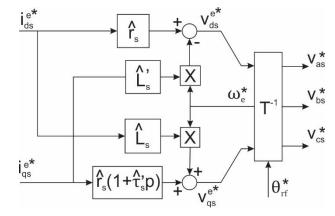

O modulador que utiliza um regulador de corrente, aplica diretamente as referências de corrente geradas no controle por orientação de campo para sintetizar as correntes de estator. Mas, é possível utilizar as tensões de terminal do motor para controlar, indiretamente, as correntes. Para isso, é necessário o uso do desacoplador de tensão da Figura 13, para que seja possível controlar, independentemente, as duas componentes das correntes do estator. A relação é obtida através da Equação 6 escrita em termos do fluxo do rotor em com eixo síncrono com o fluxo do rotor.

Figura 13 – Bloco desacoplador de tensão.

Fonte: (NOVOTNY e LIPO, 1996).

O desacoplador de tensão é fortemente dependente dos parâmetros da máquina, podendo gerar erros no cálculo do ângulo do fluxo do rotor. Por esse motivo,

o controle por histerese de corrente leva vantagem em relação a moduladores PWM que operam por tensão, pois utiliza a corrente como variável de atuação.

A seção seguinte mostra o detalhamento do controlador de velocidade e sua sintonia.

#### 2.2.1 Controlador e sintonia

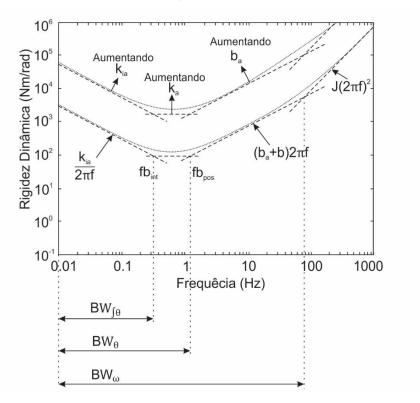

O diagrama esquemático do controle do acionamento é mostrado na Figura 14. O controlador possui uma malha de velocidade, que gera um sinal de erro e produz o sinal de comando. Uma malha de posição, é obtida através dos sinais de velocidade. Nessa configuração, os ganhos dos controladores  $b_a$ ,  $k_a$  e  $k_{ia}$  podem ser identificadas, respectivamente, como amortecimento ativo (Nms/rad), constante de mola (Nm/rad) e rejeição de perturbações em baixas frequências (Nm/s). O conjunto conversor/motor é considerado uma fonte de conjugado ideal (ganho unitário).

Figura 14 – Controlador de velocidade.

Fonte: Elaborado pelo autor, 2023.

Para a sintonia do controlador, aplica-se o conceito da rigidez dinâmica, onde quanto maior a rigidez, mais imune a perturbações de carga será o acionamento

(SCHMIDT e LORENZ, 1992). É dada pela função de transferência  $\left|\frac{T_l(s)}{\theta(s)}\right|$ , que a partir do diagrama da Figura 14 pode ser deduzida e apresentada na Equação 19.

$$\frac{T_L}{\theta} = Js^2 + (b + b_a)s + k_a + \frac{k_{ia}}{s}$$

(19)

A resposta em frequência da rigidez dinâmica é apresentada da Figura 15. Determinando-se as faixas passantes da malha de velocidade  $BW_{\omega}$ , do sinal de trajetória  $BW_{\theta}$  e da integral da trajetória  $BW_{\int \theta}$ , é possível fazer a alocação de polos da função de transferência.

Figura 15 – Resposta em frequência da rigidez dinâmica com malha de velocidade e posição.

Fonte: (SCHMIDT e LORENZ, 1992).

Além das malhas de controle por realimentação, foi acrescentado ao controlador o comando explícito, ou ação *feedforward*, antecipando-se o efeito do momento de inércia do motor, J, e o coeficiente de atrito viscoso b, utilizando-se os comandos de trajetória  $\omega^*$  e  $\alpha^*$ .

#### 2.3 Conclusão

Neste capítulo foi apresentada a teoria básica a ser aplicada na implementação do acionamento com a técnica de modulação proposta. Foram descritas as características construtivas de um conversor multinível com topologia de cinco níveis de tensão na saída, o NPC Tipo G, implementado neste trabalho, suas vantagens e desvantagens.

Outro conceito importante descrito é o do controle vetorial por orientação de campo, requisito fundamental para geração das referências de corrente que serão sintetizadas pelo inversor.

O próximo capítulo descreve a técnica de modulação proposta, apontando as dificuldades na sua implementação por meios digitais, e propondo soluções para viabilizar a sua implementação.

#### 3 CONTROLE POR HISTERESE DE CORRENTE MULTIFAIXA

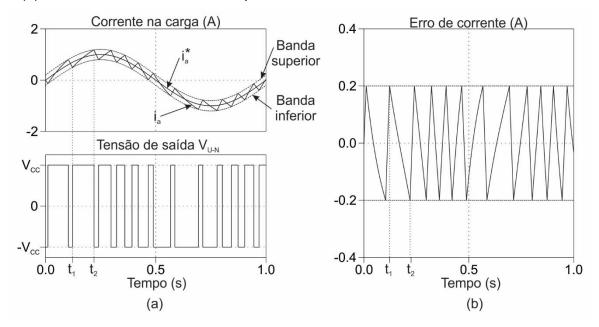

No caso de um conversor multinível há um aumento na complexidade do circuito de comando dos interruptores eletrônicos, pois o controlador deve selecionar o nível de tensão adequado a ser comutado na saída. Vários métodos de moduladores por histerese para conversores multinível são descritos na literatura. Em SHUKLA, et al., (2011) alguns dos principais métodos são mostrados e comparados entre eles, a técnica multi-offset, a baseada em tempo e a multifaixa. A estratégia multi-offset é robusta e de fácil implementação, porém, é necessário um circuito adicional para compensação do offset no sinal de erro da corrente, razão pela qual este método não é amplamente aplicado. A histerese baseada em tempo possui implementação mais complexa, sendo necessária a análise do sinal derivativo da corrente, o que pode amplificar ruídos de medição, além de ser necessário dispositivos capazes de comutar mais rapidamente. Dentre as três estratégias de modulação analisadas, a histerese multifaixa apresenta um desempenho melhor, a frequência de comutação depende das larguras de faixa de histerese, e sua complexidade na implementação pode ser contornada através do uso de dispositivos digitais. Desse modo, a histerese multifaixa foi selecionada para esse estudo, para a análise de sua viabilidade na aplicação no conversor NPC de cinco níveis, analisando suas vantagens e desvantagens.

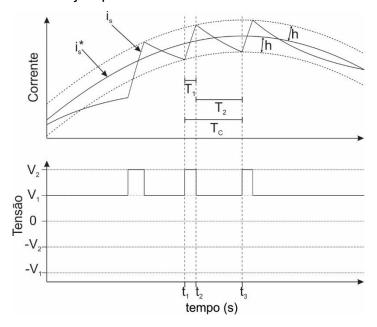

A histerese multifaixa foi apresentada pela primeira vez por MARCHESONI, (1989), e utiliza faixas de histerese simétricas para controlar a modulação, sendo uma faixa interna e mais faixas externas de acordo com o número de níveis de tensão do conversor. Assim, se um conversor possui um número n de níveis em sua saída, o comando por histerese multifaixa precisará de n-1 faixas de histerse. Sua utilização pode ser encontrada em estudos recentes como, por exemplo, a aplicação em micro redes (ELNADY e NASIR, 2022); (ELNADY e SULEIMAN, 2022), filtros ativos para eliminação de harmônicos (CHAVAN e PATIL, 2022) e acionamento de motores BLDC (RAJ, SHREELAKSHMI e GEORGE, 2020). O comportamento desse tipo de modulador é ilustrado na Figura 16 para um conversor de tensão de cinco níveis. Toda vez que o erro de corrente cruza a faixa de histerese interna h, a saída do inversor é incrementada ou decrementada de um nível de tensão, dependendo de qual limite foi cruzado e da direção da variação da corrente. Neste caso, a mudança de tensão tende a reverter o sentido do erro de corrente. Contudo, se a mudança na tensão de saída não for suficiente e a direção da corrente não se reverter, o erro continua através da

faixa h até cruzar a primeira faixa externa  $h_1$ , e nesse momento um nível de tensão mais alto (ou mais baixo) é comutado na saída. Esse processo continua até que a corrente reverta sua direção.

Tempo h h<sub>1</sub> h<sub>2</sub> h<sub>3</sub>

V<sub>DC</sub>V<sub>DC</sub>/2

-V<sub>DC</sub>/2

-V<sub>DC</sub>/2

-V<sub>DC</sub>/2

Figura 16 – Comportamento do controle por histerese de corrente multifaixa em um conversor de cinco níveis.

Fonte: (SHUKLA, GHOSH e JOSHI, 2011).

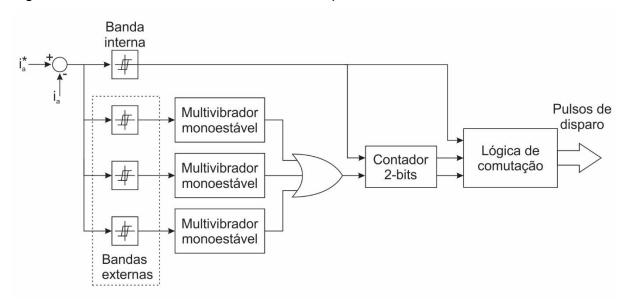

O circuito de comando para o controle por histerese multifaixa de cinco níveis está representado na Figura 17. O erro de corrente é aplicado aos comparadores de histerese das faixas interna e externas. Os sinais dos comparadores das faixas externas passam por vibradores monoestáveis para que sejam produzidos pulsos para o incremento ou decremento do contador de 2 bits, dependendo do sinal da faixa interna. O contador, por sua vez, é responsável por guardar o nível de tensão que está sendo utilizado na saída do conversor. O sinal do contador juntamente com a faixa interna produz os sinais de comando para os interruptores eletrônicos do conversor.

Figura 17 – Circuito de comando do controle por histerese de corrente multifaixa.

A histerese multifaixa, assim como outros métodos modulação por histerese, também apresenta a desvantagem da frequência de comutação variável. A Figura 18 mostra o exemplo da corrente e da tensão de saída de um inversor multinível operando com modulação por histerese de corrente multifaixa, com faixa de histerese interna h, para o acionamento de um motor de indução. Um ciclo de operação da histerese é dado por

$$T_1 + T_2 = T_C = \frac{1}{f_C} \tag{20}$$

onde  $f_c$  é a frequência de comutação.

Pela geometria da Figura 18 é possível afirmar que

$$\frac{di_{s}^{*}}{dt}T_{1} - \frac{di_{s}^{+}}{dt}T_{1} = 2h \tag{21}$$

$$\frac{di_s^*}{dt}T_2 - \frac{di_s^-}{dt}T_2 = 2h\tag{22}$$

onde  $i_s^+$  é o seguimento ascendente da corrente e  $i_s^-$  o seguimento descendente, dentro da faixa de histerese h.

Através da Equação 21, podemos afirmar que a frequência de comutação depende, entre outros fatores, da faixa de histerese h. Essa é uma característica desejável, pois, desse modo é possível utilizar o valor de h para controlar  $f_c$ .

Usando a mesma abordagem feita na seção 1.1.1, com a Equação 1 e desprezando a resistência de estator, temos

$$\frac{di_s^+}{dt} \approx \frac{V_2 - e_s}{L_s'} \tag{23}$$

$$\frac{di_s^-}{dt} \approx \frac{V_1 - e_s}{L_s'} \tag{24}$$

As Equações 23 e 24 mostram que, além da faixa de histerese h, a frequência de comutação  $f_c$  também depende dos parâmetros da máquina de indução e também das condições de acionamento, que produzem diferentes níveis da força contraeletromotriz  $e_s$ . A variabilidade da tensão aplicada no estator e de  $e_s$  faz com que a frequência de comutação seja variável, e se torne muito difícil a sua determinação por métodos analíticos. Mas essa é uma característica comum a todos os métodos de histerese de corrente.

Figura 18 – Corrente e tensão de um conversor com modulação por histerese de corrente multifaixa.

Apesar de já estar sendo implementada e estudada há algum tempo, a implementação digital da histerese multifaixa apresenta alguns desafios, como é descrito na seção seguinte.

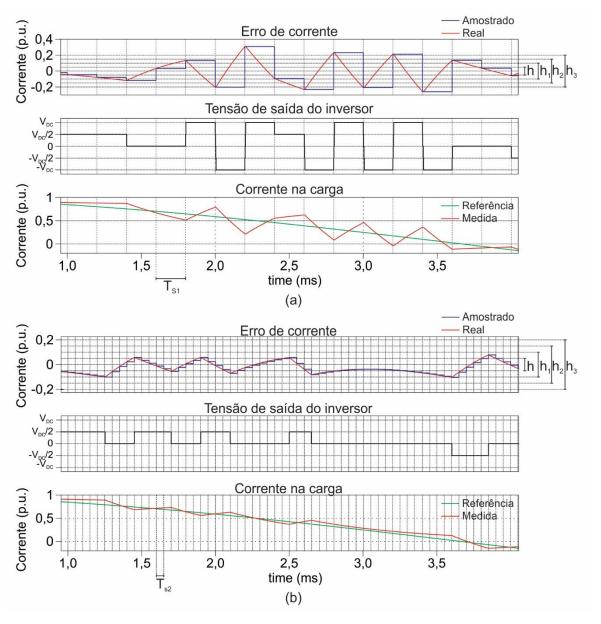

### 3.1 Histerese multifaixa digital

No controle de corrente por histerese digital, o sinal de corrente é amostrado. Desse modo, a frequência máxima de comutação do inversor é limitada à metade da frequência de amostragem (RAMOS, LUIZ, et al., 2020). Isso acontece porque o inversor atua apenas uma vez a cada intervalo entre duas amostras. Essa característica é frequentemente utilizada para limitar a frequência de comutação de um conversor controlado por histerese, porém, no caso da histerese multifaixa, essa estratégia pode comprometer a qualidade das formas de onda sintetizadas na saída do inversor. A Figura 19 mostra o comportamento da histerese multifaixa com implementação digital em duas situações, sendo a primeira (a) com uma frequência de amostragem mais baixa, e a segunda (b) uma frequência de amostragem mais alta. É possível verificar que, na primeira situação, a corrente varia de forma a cruzar mais de uma faixa de histerese externa  $(h_1 - h_3)$  dentro de um único intervalo de tempo  $T_{S1}$ entre uma amostra e outra. Nesse caso, o inversor troca, abruptamente, entre vários níveis de tensão em um só comando, chegando a trocar do nível mais baixo ao mais alto, e vice-versa, sem passar pelos níveis intermediários. Esse comportamento é indesejado e deve ser evitado. Grandes variações de tensão dv/dt podem causar danos aos dispositivos semicondutores ou à carga. A segunda situação mostra o mesmo inversor atuando com uma taxa de amostragem quatro vezes maior. Observase que, para um mesmo intervalo e mesma referência, o inversor recebe apenas comandos para a troca de níveis de tensão adjacentes. Isso ocorre porque a ação mais rápida do controlador permite que o erro de corrente mude seu sentido antes de atingir uma faixa de histerese externa.

Figura 19 – (a) Comportamento da histerese multifaixa com uma frequência de amostragem baixa, insuficiente para o funcionamento adequado e (b) com uma frequência de amostragem mais alta, que proporciona melhor aproveitamento da técnica.

Diante da característica da frequência de comutação variável própria do método do controle por histerese de corrente e, na dificuldade de se utilizar a frequência de amostragem para limitá-la, a solução proposta neste trabalho é a utilização de um circuito limitador de frequência no sinal de comando dos interruptores do inversor. Desse modo, é possível que o acionamento opere com uma taxa de amostragem mais alta, evitando o comportamento indesejado já descrito, e tenha uma proteção contra

uma frequência de comutação muita alta que possa exceder o limite dos interruptores eletrônicos. Os detalhes do circuito limitador de frequência e sua implementação são descritos na seção seguinte.

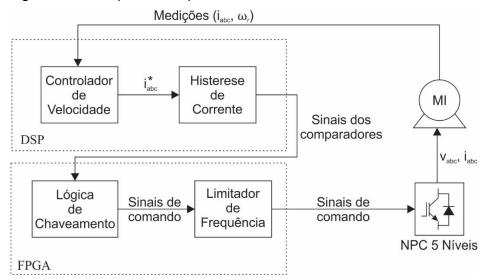

### 3.2 Circuito limitador de frequência

A Figura 20 apresenta o esquema do circuito limitador de frequência proposto. Os elementos monoestáveis geram um pulso positivo de largura fixa definida em função da frequência limite f, ou seja, a largura do pulso deve ser equivalente ao período T=1/f. Quando um pulso positivo (borda de subida) é aplicado na entrada, a saída do flip-flop RS é colocada em nível 1, o que dispara o monoestável, que por sua vez, com o auxílio das portas lógicas NOT e AND impede que um novo pulso positivo chegue até o flip-flop, até que T seja atingido. Assim, o circuito promove um atraso em um pulso de entrada que tenha uma frequência maior que a frequência limite f, ou seja, uma distância mínima entre dois pulsos positivos é garantida. A mesma lógica é aplicada para pulsos com borda de descida, limitando a frequência do sinal de entrada em f.

Entrada Saída R Q

Figura 20 - Circuito limitador de freguência.

Fonte: Elaborado pelo autor, 2023.

A Figura 21 mostra o comportamento do circuito limitador de frequência, para impor um limite de  $2.500~\rm Hz$  ao sinal de entrada. Quando um pulso é aplicado com um ciclo de  $350~\mu s$  ( $2857~\rm Hz$ ), o sinal de saída tem seu desligamento atrasado, fazendo com que o ciclo dure por  $400~\mu s$  ( $2500~\rm Hz$ ).

Figura 21 – Comportamento do circuito limitador de frequência.

Para a implementação do acionamento completo, o controle de velocidade, que gera as referências de corrente para o modulador, e o modulador devem trabalhar de maneira assíncrona com relação ao limitador de frequência. Desse modo, o circuito limitador de frequência não dependerá da frequência de amostragem do controle, permitindo sinais de comando mais precisos para os interruptores eletrônicos. Isso leva a necessidade de duas unidades de processamento independentes, como mostrado na Figura 22, onde um DSP é responsável pelo controle de velocidade e modulador por histerese, e um FPGA é responsável pela lógica de comutação e os limitadores de frequência. Caso todo o circuito lógico seja implementado no DSP, os circuitos limitadores de frequência seriam processados em sequência. Neste caso, a velocidade de processamento para os 24 interruptores eletrônicos poderia causar atrasos nos sinais de comando da mesma ordem de grandeza do tempo morto gerado nos drivers de acionamentos dos interruptores (microsegundos), podendo prejudicar a precisão desses sinais. O FPGA proporciona o processamento em paralelo para cada um dos limitadores de frequência dos 24 interruptores, promovendo uma precisão da ordem de nanosegundos para os sinais de comando. Além disso, sua atuação fica independente da frequência de amostragem do DSP.

Figura 22 – Esquema do processamento do acionamento.

#### 3.3 Conclusão

Este capítulo apresentou o método de modulação por histerese de corrente multifaixa, mostrando suas vantagens e desvantagens. Sua implementação digital apresenta algumas dificuldades que podem ser superadas através do método proposto.

A técnica proposta consiste em dissociar a frequência de amostragem da frequência de atuação do conversor. É utilizado um circuito limitador de frequência nos sinais de comando dos interruptores eletrônicos para limitar a frequência de comutação ao invés de limitar a taxa de amostragem.

O capítulo seguinte mostra os resultados de simulação e experimentais para um acionamento usando a técnica proposta.

# 4 RESULTADOS DE SIMULAÇÃO E EXPERIMENTAIS

Este capítulo apresenta resultados de simulação e experimentais que têm como objetivo avaliar o desempenho operacional da técnica de histerese digital multifaixa com limitador de frequência de comutação proposto neste trabalho.

Os resultados de simulação, apresentados na seção 4.1, foram obtidos a partir da implementação de um acionamento com máquina de indução de 6.000 hp, 4.160 V, 1.787 rpm, no software PLECS da PLEXIM. Cabe ressaltar que estes níveis de potência e tensão são justamente aqueles para os quais o conversor de cinco níveis Tipo G é mais indicado. Foi feita a implementação do controle em tempo discreto para que os resultados se aproximem da situação real, e para que possam ser feitas as discussões em relação às dificuldades de implementação digital da histerese de corrente multifaixa.